意法半導體(STMicroelectronics,簡稱ST)宣布針對高性能應用進一步擴大其廣受贊譽的SPEAr?(結構化處理器增強型架構)微處理器產品陣容。這一戰略舉措,旨在為日益復雜且要求嚴苛的計算機網絡工程設計提供更強大、更靈活、更具能效的核心計算引擎。

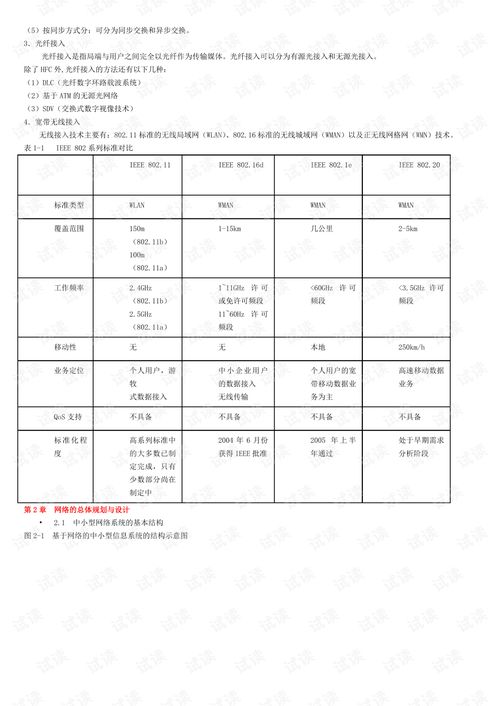

隨著云計算、邊緣計算、工業物聯網和5G通信的飛速發展,現代網絡基礎設施正面臨前所未有的挑戰。網絡設備,如高端路由器、多層交換機、網絡安全網關、網絡附加存儲以及無線接入點控制器等,不僅需要處理海量數據的快速轉發與交換,還需集成復雜的協議處理、深度包檢測、流量管理、虛擬化及安全加密功能。傳統的通用處理器或單一架構的芯片往往難以在性能、功耗、集成度和成本之間取得最佳平衡。

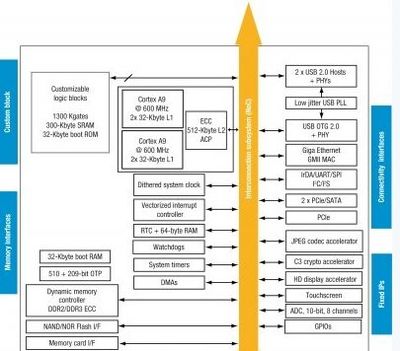

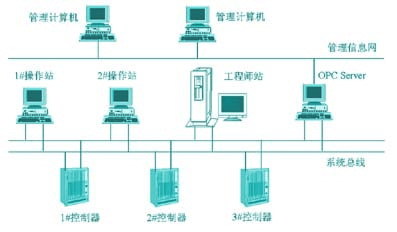

ST此次擴大的SPEAr微處理器系列,正是瞄準了這一市場痛點。SPEAr系列以其高度可配置的異構多核架構著稱,通常集成了高性能的ARM應用處理器內核、專用的網絡協處理單元以及豐富的高速接口。新的產品陣線預計將在以下方面為計算機網絡工程設計帶來革新:

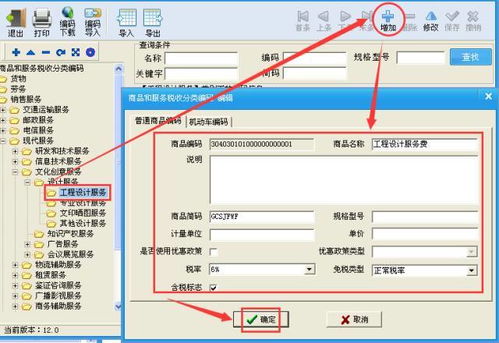

- 性能躍升與能效優化:新器件將采用更先進的制程工藝,集成更高主頻的多核ARM Cortex-A系列處理器,并強化硬件加速引擎。這使得設備在運行路由協議棧、防火墻規則、VPN加解密等任務時,能夠實現極高的吞吐量和極低的延遲,同時保持優異的每瓦特性能比,滿足綠色數據中心和邊緣節點的節能需求。

- 高度集成與設計簡化:新產品將提供更豐富的外設接口集成,如多端口萬兆以太網控制器、PCIe Gen3/4接口、USB 3.0、SATA 3.0等。這種高度集成的SoC(片上系統)設計,極大減少了工程師所需的外部元件數量,簡化了電路板布局,縮短了產品開發周期,并降低了整體系統成本與功耗。

- 增強的靈活性與可編程性:SPEAr架構的“結構化”特性意味著,工程師可以根據特定的網絡應用需求,靈活配置硬件加速模塊與軟件任務的分工。專用的可編程包處理引擎或硬件加速器能夠卸載CPU的繁重負載,讓CPU更專注于控制平面和管理任務。這種軟硬件協同設計模式,為網絡設備制造商提供了巨大的差異化創新空間。

- 強化安全功能:網絡安全是網絡設計的基石。新的SPEAr處理器預計將內置更強大的硬件安全模塊,支持可信執行環境、安全啟動、加密算法加速以及防篡改機制,從芯片層面為網絡設備構筑堅實的安全起點,符合日益嚴格的市場法規要求。

對計算機網絡工程設計的影響

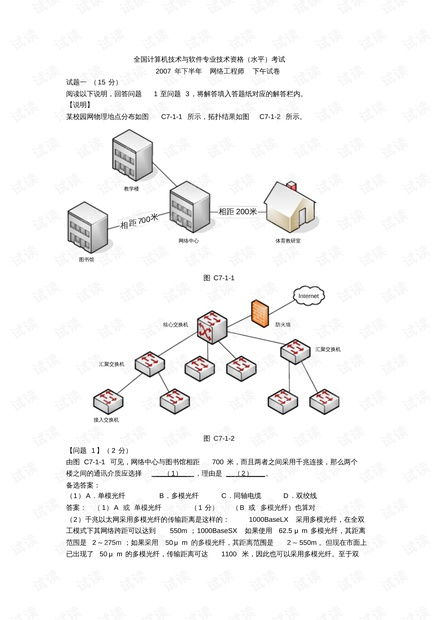

對于網絡設備設計工程師而言,ST擴大SPEAr產品線意味著擁有了更多樣化的核心平臺選擇。在設計下一代企業級交換機、運營商級接入設備、智能網卡或網絡安全設備時,工程師可以:

- 精準匹配性能需求:從中小型企業到大型數據中心,不同層級的網絡設備都能找到性能與成本相匹配的SPEAr解決方案。

- 加速產品上市:借助ST提供的完整參考設計、軟件開發套件和成熟的軟件生態系統,可以大幅減少底層驅動和基礎協議的開發工作,將精力集中于高附加值的功能創新。

- 實現前瞻性設計:芯片強大的處理能力和接口擴展性,使得設計的設備能夠平滑適應未來網絡協議升級和帶寬增長的需求,保護投資。

ST擴大其SPEAr微處理器產品陣線,不僅鞏固了其在嵌入式網絡處理市場的領先地位,更是為應對未來網絡挑戰提供了關鍵的半導體解決方案。通過將高性能計算、高度集成、硬件加速和增強安全性融為一體,新的SPEAr系列有望成為推動下一代高性能、高效率、高安全網絡設備設計與創新的核心動力,助力全球計算機網絡工程向更智能、更敏捷、更可靠的方向演進。